当ChatGPT掀起全球AI浪潮时,很少有人注意到:这场算力革命的底层,不只有GPU和算力,还有电。

据TrendForce预测,2025年全球AI服务器出货量将突破246万台,同比增长24.3%。单颗GPU功耗从数百瓦跃升至700W、1000W甚至2000W——这意味着芯片需要的供电电流已达到千安级(600A–1500A)。

供电设计不再是后端考虑的问题,而是已成为影响AI芯片设计和制造方式的前沿制约因素。

本文将从AI算力场景出发,深入解析DCDC转换器与LDO稳压器面临的新要求,以及国产电源芯片的应对策略。

AI芯片进入千瓦级时代,传统的分立式DCDC方案已难以满足功率密度要求。工程师们开始向以下方向突破:

集成化:将控制器、MOSFET、电感集成于单一封装

3D堆叠:近芯片端供电+垂直集成基板,缩短供电路径

据行业数据,为缩短供电路径、降低阻抗、减少损耗并提升瞬态响应,行业已向近芯片端供电+垂直集成方向演进。

AI推理芯片(如Jetson Xavier NX)在推理时会产生50mA至2A的动态负载跳变,这对DCDC的瞬态响应提出了极高要求:

技术路径:数字控制、TCM/CCM交错控制、图腾柱PFC技术

希荻微等国内厂商已推出具备”全球一流负载瞬态响应”的AI服务器供电芯片,输出电流高达50A,效率超过90%。

更高开关频率意味着更小的被动元件体积,但也带来更严峻的EMI挑战。AI服务器通常部署于数据中心密集环境,电磁干扰会直接影响其他IT设备的稳定性。

展频技术(Spread Spectrum):分散谐波能量

单相DCDC已无法满足AI芯片的供电需求,多相并联成为标配:

AI服务器的运维需要预测性维护,这要求DCDC具备:

AI推理芯片对电源噪声极为敏感。以神经网络权重量化精度(INT8/FP16)为例:

电源噪声电压需<5μVrms(10Hz-1MHz带宽),否则会导致激活函数计算偏差,推理准确率下降。

这是什么概念?传统LDO的噪声通常在数十μVrms级别,而AI场景要求降低一个数量级。

AI芯片工作频率高、电流变化快,来自前级DCDC的纹波会直接影响后级LDO的输出纯净度。

共模半导体GM1200系列已实现120dB@1kHz、90dB@10kHz的超高PSRR,可完美适配AI推理场景。

即使静态噪声达标,瞬态过程中的下冲/过冲同样会干扰AI芯片。

边缘AI设备(如AI摄像头、无人机)通常采用电池供电,要求LDO在低压差条件下仍能保持高效率:

48V总线 → DC/DC(48V→12V/5V) → POL DCDC(12V→1.xV) → LDO(为ADC/时钟/传感器供电)

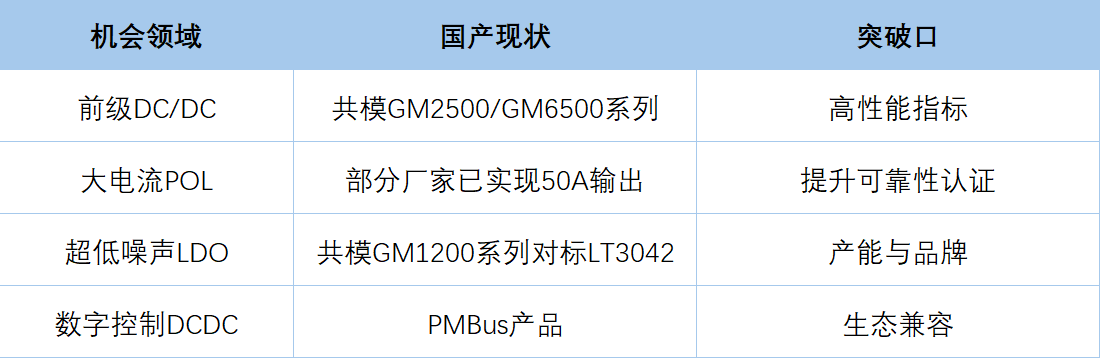

当前AI服务器电源市场仍以TI、ADI、Infineon等国际大厂为主导。然而,国产替代的窗口正在打开:

边缘AI设备(如AI摄像头、无人机)通常采用电池供电,要求LDO在低压差条件下仍能保持高效率:

车规/工规认证周期长:AI数据中心虽非车规,但可靠性要求同样严苛

生态兼容:与Intel/AMD/NVIDIA平台的VRM兼容性验证

产能保障:大规模AI服务器部署对供应链的稳定性要求极高

4.1 垂直供电网络(VPD):从”平面”到”立体”

传统供电网络(PDN)采用平面布线,背面供电网络(Backside Power Delivery)正在成为AI芯片的下一代方案:

高功率密度下,液冷与功率器件的热协同设计将成为必修课:

4.1 垂直供电网络(VPD):从”平面”到”立体”

AI算力的爆发式增长,正在倒逼电源技术进行全面重构。从DCDC的千瓦级功率密度、纳秒级瞬态响应,到LDO的微伏级噪声、百兆赫兹PSRR——每一个参数都在逼近物理极限。

这是一场没有终点的技术竞赛。

对国产电源芯片而言,AI浪潮既是挑战,更是千载难逢的替代窗口。唯有在核心参数上实现对标乃至超越,才能在这场全球竞速中占据一席之地。

共模半导体将持续深耕高性能电源赛道,为AI算力时代提供”芯”级动力。